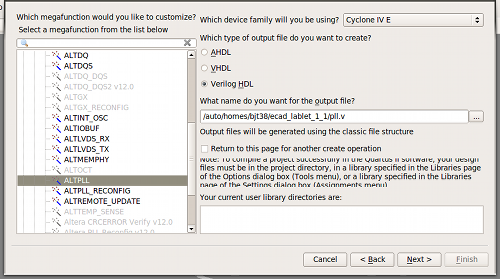

Simple dual-port memory mode with different read and write port widths. Simple dual-port memory supports a simultaneous read and write. Single-port memory supports non-simultaneous reads and writes. Memory Mode Single-port memory Simple dual-port memory Simple dual-port with mixed width True dual-port memory True dual-port with mixed width Embedded shift register ROM FIFO buffers Description M4K blocks support single-port mode, used when simultaneous reads and writes are not required. true dual) From Cyclone II documentation. EECS 452 Fall 2014 Lecture 5 /143 Tuesday September 16, 2014ġ5 M4K RAM Table 2 7. A design making heavy use of bit-serial arithmetic likely would choose a Xilinx FPGA over an Altera FPGA. Xilinx s (but not Altera s) LUTs support use as a 16 bit shift register. The Cyclone II does not support use of a LE s LUT as memory.

Each LE contains a D-register that can be used as a one-bit memory. Can t necessarily use as one large block. All registers need to be clocked at the same instant to prevent unwanted race conditions and incorrect loading due to propagation delays in the combinatorial logic. Between clock tics, combinatorial logic is used to determine the next contents of the registers.

wiki/register-transfer_level The state of a design is contained in registers that are all clocked at the same time. EECS 452 Fall 2014 Lecture 5 /143 Tuesday September 16, 2014ġ3 Clock distribution network Modern logic design is largely based on the register transfer level (RTL) paradigm. 12 Programmable interconnections Programmable routing is a large part of configurable.

0 kommentar(er)

0 kommentar(er)